## 3 - 27 Worst-case Supply Voltage for Single Event Upset Performance of Commercial SRAM Devices

Zhang Zhangang, Liu Jie, Hou Mingdong, Sun Youmei, Gu Song, Liu Tianqi, Tong Teng Wang Xiaohui, Su Hong, Yao Huijun, Luo Jie, Geng Chao and Xi Kai

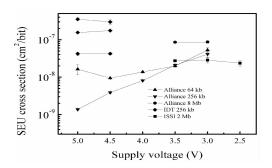

Fig. 1 The SEU cross sections plotted as a function of supply voltage for five DUTs.

The single event upset (SEU) sensitivity of digital devices depends on several factors and supply voltage is one of the key parameters which can affect the inner electrical field and also critical charge. In 1992, L. R. Hite<sup>[1]</sup> reported increased SEU sensitivity of SOI SRAM with higher voltage, which is attributed to the amplification of primary collected charge by the parasitic bipolar transistor. More recently, F. El-Mamouni<sup>[2]</sup> pointed out that higher drain bias increases the amplitude of the drain current transients of bulk Fin-FET, but with unchanged total collected charge. On the other hand, constant reduction of supply voltage of modern semiconductor devices results in a decrease of the electrical charge used to store logical value<sup>[3]</sup>, which leads to worse

SEU performance. The net contribution of those competing mechanisms to the SEU sensitivity should be investigated in different kinds of memory.

In the experiment, SRAMs from several companies with various capacitieswere irradiated at HIRFL by using <sup>12</sup>C, <sup>40</sup>Ar, <sup>86</sup>Kr and <sup>209</sup>Bi ions with initial energy of 7, 25, 25 and 9.5 MeV/u, respectively. The SEU cross sections of those devices under test (DUTs) were measured at supply voltages within the operating power supply range. As shown in Fig. 1, as supply voltage decreases the SEU cross sections of Alliance 64 kb and 256 kb SRAMs increase significantly. Alliance and ISSI memories were irradiated by <sup>12</sup>C beam with a LET value of 2.4 MeV/(mg/cm²). IDT 256 kb SRAM was irradiated by <sup>40</sup>Ar, <sup>86</sup>Kr and <sup>209</sup>Bi beam with LET values of 7.6, 28.6 and 100 MeV/(mg/cm²), respectively. The reduction of critical charge is the predominant factor worsening the device performance. While for other devices, no obvious trend is observed which is attributed to the negligible net contribution of those competing mechanisms. Those experimental results indicate that the worst-case supply voltage for SEU sensitivity depends on the test device.

## References

- [1] L.R. Hite, H. Lu, T.W. Houston, et al., IEEE Trans. Nuc. Sci., 39(1992)2121.

- [2] F. El-Mamouni, E. X. Zhang, D. R. Ball, et al., IEEE Trans. Nuc. Sci., 59(2012)2674.

- [3] S. Uznanski, G. Gasiot, P. Roche, et al., IEEE Trans. Nuc. Sci., 58(2011)2652.